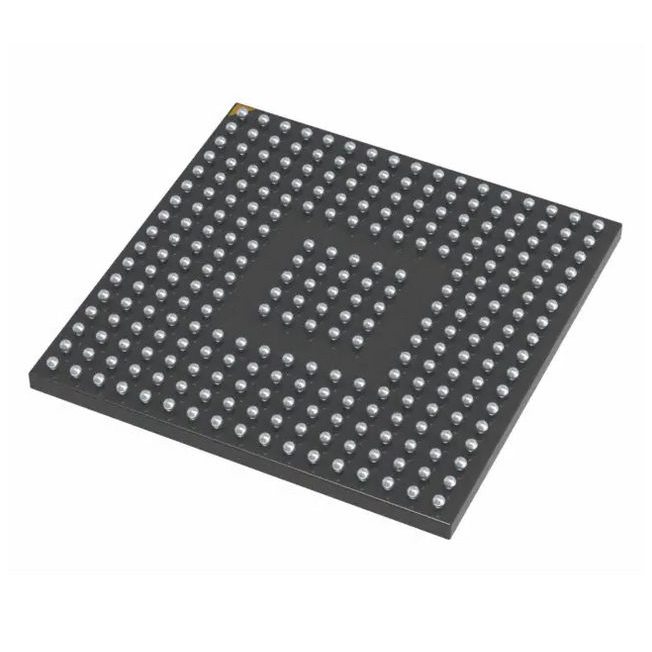

ISPLSI5384VE-165LF256 - Brand New LATTICE Programmable Logic Device (CPLDs/FPGAs)

-

ispLSI 5000VE Description

The ispLSI 5000VE Family of In-System Programmable High Density Logic Devices is based on Generic Logic Blocks (GLBs) of 32 registered macrocells and a single Global Routing Pool (GRP) structure interconnecting the GLBs.

Outputs from the GLBs drive the Global Routing Pool (GRP) between the GLBs. Switching resources are provided to allow signals in the Global Routing Pool to drive any or all the GLBs in the device. This mechanism allows fast, efficient connections across the entire device.Features

• Second Generation SuperWIDE HIGH DENSITY IN-SYSTEM PROGRAMMABLE LOGIC DEVICE

— 3.3V Power Supply

— User Selectable 3.3V/2.5V I/O

— 18000 PLD Gates / 384 Macrocells

— Up to 192 I/O Pins

— 384 Registers

— High-Speed Global Interconnect

— SuperWIDE Generic Logic Block (32 Macrocells) for Optimum Performance

— SuperWIDE Input Gating (68 Inputs) for Fast Counters, State Machines, Address Decoders, etc.

— PCB Efficient Ball Grid Array (BGA) Package Options

— Interfaces with Standard 5V TTL Devices

• HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— fmax = 165 MHz Maximum Operating Frequency

— tpd = 6.0 ns Propagation Delay

— TTL/3.3V/2.5V Compatible Input Thresholds and Output Levels

— Electrically Erasable and Reprogrammable

— Non-Volatile

— Programmable Speed/Power Logic Path Optimization

• IN-SYSTEM PROGRAMMABLE

— Increased Manufacturing Yields, Reduced Time-toMarket, and Improved Product Quality

— Reprogram Soldered Devices for Faster Debugging

• 100% IEEE 1149.1 BOUNDARY SCAN TESTABLE AND 3.3V IN-SYSTEM PROGRAMMABLE

• ARCHITECTURE FEATURES

— Enhanced Pin-Locking Architecture with SingleLevel Global Routing Pool and SuperWIDE GLBs

— Wrap Around Product Term Sharing Array Supports up to 35 Product Terms Per Macrocell

— Macrocells Support Concurrent Combinatorial and Registered Functions

— Macrocell Registers Feature Multiple Control Options Including Set, Reset and Clock Enable

— Four Dedicated Clock Input Pins Plus Macrocell Product Term Clocks

— Programmable I/O Supports Programmable Bus Hold, Pull-up, Open Drain and Slew Rate Options

— Four Global Product Term Output Enables, Two Global OE Pins and One Product Term OE per Macrocell -

Similar parts: 2518 , Click to view

-

Datasheet

-

Shopping guide

Delivery period:

- - Will ship out in 2-3 days

- - DHL Express: 3-7 business days

- - DHL eCommerce: 12-22 business days

- - FedEx International Priority: 3-7 business days

- - EMS: 10-15 business days

Shipping fee:

- - Automatic Email notification (above 5 times)

- - View in your order page

Shipping option:

DHL, FedEx, EMS, SF Express, and Registered Air MailShipping tracking:

- - Automatic Email notification (above 5 times)

- - View in your order page

How to Buy:

- - In-stock, Add to cart > Check out > Submit order > Complete payment >Delivery.

- - Inquiry, Add to inquiry sheet/Submit bom/inquire file/Send email us > Quote > Place order > Complete payment >Delivery.

- View more

Payment:

- - Paypal,Credit Card includes Visa, Master, American Express.

- - Wire transfer, include Local bank transfer.

- - Western Union.

- View more

- Datasheet: Download ISPLSI5384VE-165LF256

- Chipdatas Part: CD89-ISPLSI5384VE-165LF256

- Warehouse: China, Hong Kong

- Dispatch: Within 24 hours

- Free Shipping: Yes

- Prority Shipping: Yes, 3-5 days

- Last Updated: 2024/10/01 19:53 +0800

-

- Full Refund if you don't receive your order

- Full or Partial Refund , If the item is not as described

-

The fee is charged according to the rule of PayPal.

-

The fee is charged according to the rule of PayPal.

-

Western Union charge US$0.00 banking fee.

-

We recommend to use bank transfer for large orders to save on handling fees.

-

DHL(www.dhl.com)

$40 limited time offer. -

UPS(www.ups.com)

$40 limited time offer. -

FedEx(www.fedex.com)

$40 limited time offer. -

Registered Mail(www.singpost.com)

Free shipping without minimum order.